# ディレイラインテクニカルシート

# Delay Line Technical Sheet

# <ディレイライン・テクニカルシート>

# 目 次

- (1) はじめに

- (2) ディレイライン

- (3) ディレイラインの構成

- (4) ディレイラインに求められる性能とその機能

- (5) ディレイラインにおけるパルス波形の定義

- (6) ディレイラインの計測システム

- (7) ディレイラインの技術用語とその意味

- (8) ディレイラインモジュール

- (9) プログラマブル・ディレイラインモジュール

- (10) ディレイラインのアプリケーション

- 1) 基本的な応用例

- 2) パルス幅の変換

- 3) ディレイラインを用いた発信器

- 4) アドレスデータラッチ機能を持たせたプログラマブル ディレイライン

- 5) ディレイラインと各種ロジックファミリとのインターフェース

- 1) TTL,CMOSおよびECLロジックゲート

- II) ディレイラインと差動型ドライバ・レシーバとの インターフェース

- 6) ディレイラインによるマルチプライヤー

- 7) 周波数ディスクリミネータ

- (11) おわりに

- (12) ディレイライン・カスタム仕様パラメータシート

#### (1) はじめに

このテクニカルシートは、ディレイラインの採用およびアプリケーションの検討をされている方々の参考になるように作成いたしました。ご活用いただければ幸いに存じます。本冊子は先に発行しました弊社『ディレイラインテクニカルシート D001A』を改定追補したものです。

#### (2) ディレイライン

ディレイラインまたは遅延線と呼ばれるものは、本質的に電気信号の伝播を遅くする機能を持っている部品またはデバイスのことを指します。歴史的には、レーダーの開発に必要とされ研究されました。後にコンピュータの開発に伴い電子交換機、医用機器、原子力計装機器、宇宙開発機器、放送機器などのアナログ回路・ディジタル回路に応用されています。ディレイラインの中には、超音波の伝播を利用したもの、磁歪振動の伝播を利用したもの、半導体デバイスを利用したものなど各種ありますが、ここでは現在最も用いられているインダクタンスとキャパシタンスで構成されるディレイライン(電磁遅延線)、およびこれらと半導体デバイスを組み合わせて機能を付加したディレイ機能モジュールについて述べます。

# (3) ディレイラインの構成

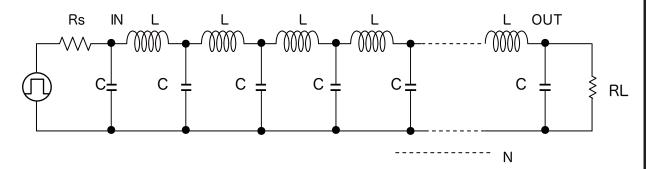

ディレイラインの一般的な回路構成は図1のような、はしご型の伝送回路網で構成されています。

図1 ディレイラインの構成

回路構成は伝送回路網における影像パラメータによる設計と動作パラメータによる設計方法がありますが、いずれも伝送インピーダンス、伝送遅延時間および伝送周波数特性を持つ伝送回路網で構成されている受動回路です。

同軸ケーブルは1mあたり約5nsの遅延時間を持ちますが、言わば同軸ケーブルを集中定数で置き換えたような伝送路と考えられます。LCの区間段数の制限から同軸ケーブルほど伝送周波数特性は良くありませんが、大きい遅延時間を得ることができます。このことは、小型にできることであり電子部品として実現できる自由度が大きいことを意味しています。遅延時間は図1でINの点からOUTの点に電気信号が伝わるまでの時間です。アナログ回路・ディジタル回路ともに異なる経路からの信号のタイミングを合わせが必要なときがあります。

また逆に時間差をつける信号処理が必要なときもあります。電気信号の伝送スピードを速めることはできませんので、遅らせたい経路にディレイラインを入れて所定の時間だけ遅らせて2つの電気信号のタイミングを合わせたり、時間差を得るためにディレイラインが必要となります。

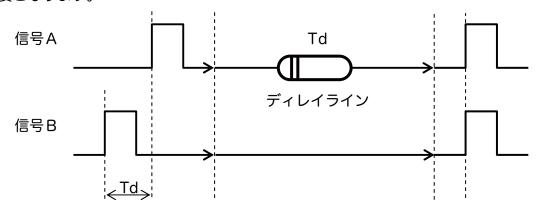

図2 ディレイラインによるタイミング合わせ

信号Aと信号Bとの時間差(Td)と等しい遅延時間を持つディレイラインを信号Aの経路に入れて、信号Aと信号Bのタイミングを合わせます。

### (4) ディレイラインに求められる性能とその機能

- 1) ディレイラインに求められる性能

- a) 正確な遅延時間

- b) 周波数特性、位相特性が良いこと

- c) 特性インピーダンスが一定で伝送信号の反射が少ないこと

- d) 減衰量(伝送損失)が少ないこと

- e) 温度特性が良いこと

### 2) ディレイラインの機能

- a) DC~数100MHz程度の信号の遅延伝送

- b) 一時的なパルス情報、アナログ情報の記憶保持

- c) エネルギーの一時的な蓄積

- d) 波形変換および符号化

主にこれらの機能を活かし、アナログ回路・ディジタル回路に応用されています。

# (5) ディレイラインにおけるパルス波形の定義

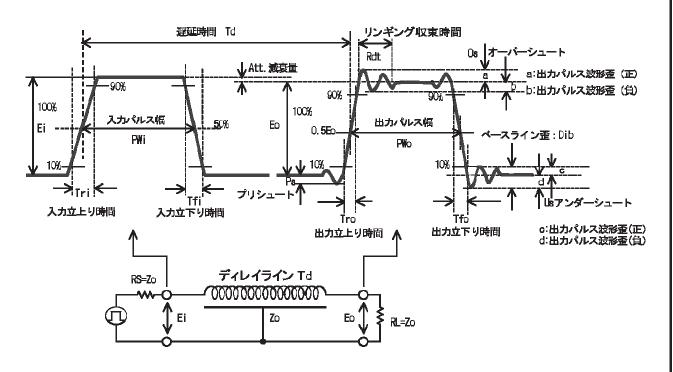

ディレイラインはアナログ信号の伝送もできますが、主にパルス波形の伝送に使用されま すので、パルス波形を定義し時間領域での表現で規格化し、仕様を決めています。 高精度のアナログ信号伝送用のディレイラインは周波数領域での規格化が求められます。 パルス波形全体を数値的に規格化して表すことはできませんが、波形の定義を規定することにより、特別でない限りディレイラインの特性を数値化して表すことができます。

図3 ディレイラインにおけるパルス波形の定義

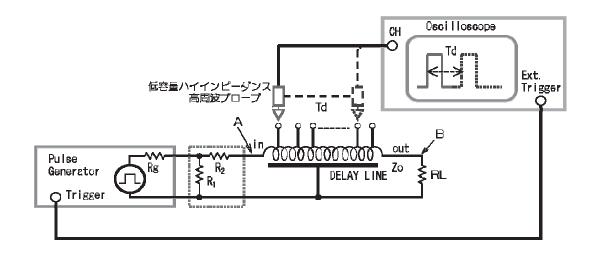

### (6) ディレイラインの計測システム

図4 ディレイラインの計測システム

特性インピーダンスZo( $\Omega$ )のディレイラインを計測するとき、パルスジェネレータの駆動インピーダンスと終端抵抗はディレイラインの特性インピーダンスに合わせなければなりません。一般にパルスジェネレータの出力インピーダンスは $SO(\Omega)$ であり、ディレイラインの特性インピーダンスに等しくありません。そのため図 $AOR_1$ と $R_2$ による最小ロスの抵抗ネットワークで整合します。 $R_1$ 、 $R_2$ および $R_L$ を次式で求めます。

$$R_L = Z_0$$

(Ω) 式[1]

$$R_1 = R_g \sqrt{\frac{Z_0}{Z_0 - R_g}}$$

(\Omega)  $\pi \pi [2]$   $R_2 = \sqrt{Z_0(Z_0 - R_g)}$  (\Omega)  $\pi [3]$

# (7) ディレイラインの技術用語とその意味

1) 特性インピーダンス *Zo* (Ω)

ディレイラインは同軸ケーブルのような伝送路であるため固有の伝送インピーダンスを持っています。その特性インピーダンスは「図1ディレイラインの構成」のインダクタンスとキャパシタンスで、式[4]のように決められます。

$$Z_0 = \sqrt{\frac{L}{C}} = \sqrt{\frac{\sum_{i=1}^{N} Li}{\sum_{i=1}^{N} Ci}} \quad (\Omega) \quad \vec{\Xi}[4]$$

波形歪や反射を少なく伝送するために、特性インピーダンスが均一であることが重要です。

2) 遅延時間 *Td*(s)

遅延時間は、図1の回路で概ね式[5]で求められます。

$$Td = N\sqrt{LC} = \sqrt{\sum_{i=1}^{N} Li \times \sum_{i=1}^{N} Ci} \qquad (s) \quad \vec{x}[5]$$

1区間の遅延時間は $\sqrt{LC}$ で決まり、全体の遅延時間は区間imes段数 Nとなります。

3) 立上り時間 *Tro* (s)

ディレイラインの固有の立上り時間は、そのディレイラインの上限の伝送帯域により制限されます。「図4 ディレイラインの計測システム」において、オシロスコープの伝送帯域が十分広く、パルスジェネレータの立上り時間が十分速く、テストフィクチュアの浮遊容量および残留インダクタンスが少なく、グランドインピーダンスが低い高周波数計測に適したものであることなどが必要です。これらの条件を満たしているとき、計測対象のディレイラインの固有特性が計測されます。パルス応答波形は計測システムのこれらの条件で異なりますので、計測精度、再現性を重視する場合は、これらの検討が必要です。測定手順として、はじめにテストフィクチュアにディレイラインを実装しない状態で整合回路端を終端抵抗 $R_L$ で終端します。このとき観測される立上り時間がディレイラインの入力に与えられる立上り時間 Triとなります。

立上り時間は一般に図3のパルス前縁の振幅が10%から90%に遷移する経過時間と定義しています。立下り時間 Tfiはパルスの後縁の振幅が90%から10%に遷移するまでの経過時間となります。

次にテストフィクチュアにディレイラインを実装し、「図4 ディレイラインの計測システム」により、ディレイラインの最大遅延時間端子で観測される立上り時間 *Tro* を計測します。このときのディレイライン固有の立上り時間 *Trt* は、式[6]で求められます。

$$T_{rl} = \sqrt{T_{ro}^2 - T_{ri}^2}$$

(s)  $\pm$ [6]

この計算が必要となるのは Tro に対して Triが無視できない値を持つときです。 一般には Tri < Tro ですから、 Trt = Tro となります。したがって式[6]の手順は省略できます。

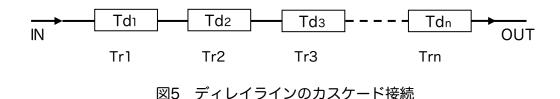

図5のように整合をとってディレイラインをカスケードにn個接続した場合の総合した立上り時間 Tro および遅延時間 Tdo は次のように表すことができます。

$$T_{ro} = \sqrt{T_{r1}^2 + T_{r2}^2 + \cdots + T_{rn}^2} = \sqrt{\sum_{i=1}^n T_{ii}^2}$$

(s)  $\vec{x}$ [7]

$$T_{do} = T_{d1} + T_{d2} + \dots + T_{dn} = \sum_{i=1}^{n} T_{di}$$

(s)  $\vec{\Xi}[8]$

また、ディレイラインの周波数特性は緩やかに減衰するので、立下り時間 Tfo は、ほぼ立上り時間 Tro に等しくなります。

# 4) 立上り時間と伝送周波数帯域

ディレイラインの立上り時間はそのディレイラインの伝送帯域の上限周波数に支配され、その関係は式[9]で表すことができます。上限の遮断周波数を fc(Hz)とします。

$$f_c = \frac{1}{T_r} \sqrt{\frac{\ln 2}{2 \, \pi}} = \frac{0.332}{Tr} \approx \frac{0.35}{Tr}$$

$T_r = \frac{0.35}{f_c}$   $\vec{\pi}$ [9]

例1 立上り時間10(ns)のときの上限遮断周波数は、式[9]より次のように求められます。

$$f_c = \frac{0.35}{10 \times 10^{-9}} = 35 \times 10^6 = 35$$

(MHz)

# 5) 立上り時間と伝送パルス幅および減衰量

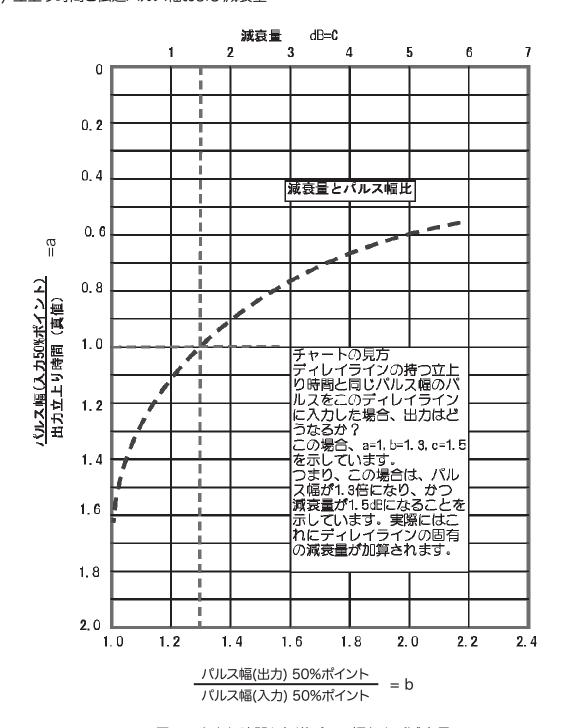

図6 立上り時間と伝送パルス幅および減衰量

ディレイラインの持つ立上り時間により最小伝送パルス幅が制限されます。狭いパルス幅ほど高い周波数成分を持っていますので、立上り時間の速いことが求められます。 パルス幅 Pw と必要な伝送周波数帯域の関係は、およそ式[10]のようになります。

$$f_c \approx \frac{1}{P_w}$$

(Hz) 式[10]

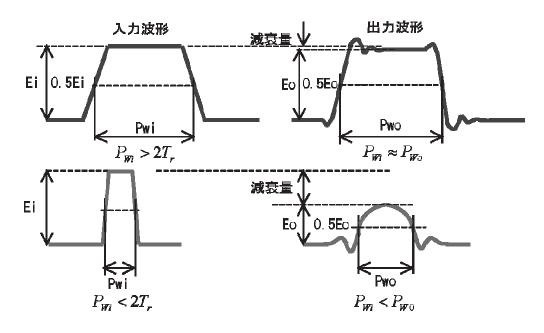

図6はある立上り時間を持つディレイラインに、あるパルス幅のパルスを入力したとき、 出力端でのパルス幅とその減衰量の関係を示しています。逆にあるパルス幅を持つパル スを遅延させるために必要なディレイラインの立上り時間を求めることもできます。 ディレイラインを無理なく通過するパルス幅は少なくともディレイラインの持つ立上り 時間の3倍以上のパルス幅が必要です。立上り時間と伝送パルス幅の関係が、*Pw < 2Tr* の条件では入力パルスに対して出力パルスは減衰します。そして、振幅の50%点での パルス幅は入力パルス幅より広がります。

この現象をパルス・ストレッチング(Pulse Stretching)と呼んでいます。

図7はこれらの関係を示したものです。

図7 ディレイラインの立上り時間とパルス応答

例2パルス幅50nsのパルスを減衰量0.5dB以下で伝送するために必要なディレイラインの立上り時間を求めます。

図6より、*Tr*=50ns/1.28=39ns となります。立上り時間39nsのディレイラインを使用する応答出力パルス幅は約50ns×1.1=55ns となります。出力幅の85% になる入力パルス幅は、ディレイラインとして動作するほぼ限界と考えられます。

$$P_{w}(\min) = T_{r} + \frac{(T_{fi} - T_{ri})}{2}$$

(s)  $\vec{x}[11]$

Pw (min): 伝送最少入力パルス幅 (s) Tr: ディレイライン立上り時間 (s)

Tfi

入力パルス立下り時間 (s)

Tri

入力パルス立上り時間 (s)

Tfi = Tri のとき、Pw (min) = Tr これは図6の例に相当します。 これらの関係から、逆に応答パルス幅を計測して立上り時間を求めることもできます。

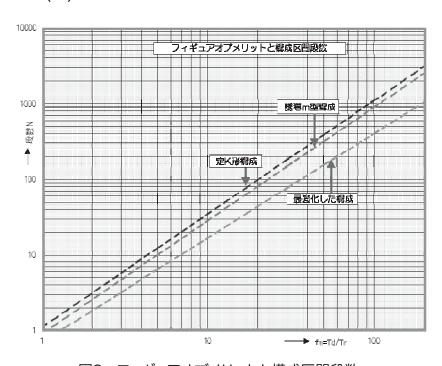

6) フィギュアオブメリット (Figure of Merit) ここでのフィギュアオブメリットとは、ディレイラインの良さを表わす指数です。この 指数は、ディレイラインの全遅延時間 *Td* と立上り時間 *Tr* の比で表わします。

$$f_m = \frac{Td}{Tr}$$

式[12] この指数は「図1ディレイラインの構成」において、

LCのはしご型回路の段数Nとこの指数との関係は次のような関係で表わすことができます。

$$N = k \left( fm \right)^n = k \left( \frac{Td}{Tr} \right)^n$$

式[13] ここで、 $k \ge n$  は回路構成により決まる

定数です。一般には、同じ指数 fmであるなら Nが小さい方が優れた回路構成ということになります。ちなみに図1のような定 k 形回路構成では、

$$N=1.1\times\left(\frac{Td}{Tr}\right)^{1.5}$$

$k=1.1$   $n=1.5$  となり、誘導  $m$ 形構成では、

$$N = 0.9 \times \left(\frac{Td}{Tr}\right)^{1.5}$$

$k = 0.9$   $n = 1.5$  となります。

コア材料とその形状を適正化し、コイル間の結合を最適化した回路構成では、

$$N=0.7\times\left(\frac{Td}{Tr}\right)^{1.38}$$

$k=0.7$   $n=1.38$  となります。

図8 フィギュアオブメリットと構成区間段数

いずれの構成法でも fm は、全遅延時間 Td と立上り時間 Tr の比の指数になっています。 この値が大きいと、Nは非常に大きくなります。

# 7) 遅延時間 (Delay Time)

全遅延時間 Td は、「図4 ディレイラインの計測システム」および「図3 ディレイラインにおけるパルス波形の定義」において、遅延時間の3倍以上のパルス幅のパルス信号を入力端子に与えたとき、入力端子から最終出力端子に伝達されるまでの時間です。入出力パルスのそれぞれの前縁50%点間を計測します。

端子間遅延時間 Tdt (タップ間遅延時間)は、回路接続において隣り合った端子間のパルス信号の伝播時間です。

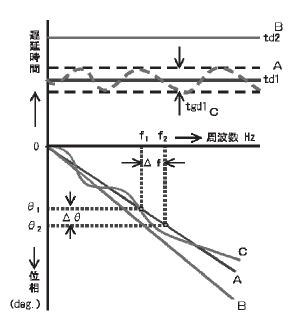

周波数に対する遅延時間の偏差を群遅延時間 *Tdg* と呼んでいます。これは周波数に対する位相偏差によります。群遅延時間は次式[14]で表わすことができます。

$$Tdg = -\frac{d\theta (rad)}{d\omega (rad/s)} = -\frac{1}{360} \frac{\theta (\deg)}{f(Hz)}$$

(s)  $\vec{x}[14]$

また、位相遅延時間 Ptd は次のように表わすことができます。

$$Ptd = -\frac{\theta (rad)}{\omega (rad/s)} = -\frac{1}{360} \frac{\theta (\deg)}{f (Hz)}$$

(s)  $\vec{x}$ [15]

これらの関係を図9に示します。

図9 群遅延時間と位相の関係

周波数に対して位相がリニアであれば群遅延時間と位相遅延時間は同じ値になります。 このとき周波数に対する位相の傾きが、群遅延時間になります。したがって周波数に対する位相がリニアでないと群遅延時間が変動します。波形伝送ではこの位相ひずみにより、周波数スペクトラムが拡散されひずみを生ずる原因となります。高精度の遅延伝送では、図9におけるtgd1の偏差は小さいことが求められます。つまり群遅延時間特性が良好であることになります。

# 8) 減衰量 (Attenuation)

図4のディレイラインの計測システムにおいて、ディレイラインの持つ立上がり時間の3倍以上のパルス幅を持つパルスを入力し、図3における入力振幅電圧 *Ei*と出力電圧 *Eo*との差で表します。

$$Att = \frac{Ei - Eo}{Ei} \times 100$$

(%) または  $Att = 20 \log \left| \frac{Ei - Eo}{Ei} \right|$  (dB) 式[16]

# 9) ディストーション (Distortion)

図3における出力波形歪みの量を示します。このディストーションは、入力パルスの立上がり時間・計測冶具により支配されますので、これらの条件を決めて計測する必要があります。

振幅ライン歪

$$Dia = \frac{a}{Eo} \times 100$$

(%) または  $Dia = \frac{b}{Eo} \times 100$  (%) 式[17]

ベースライン歪

$$Dib = \frac{c}{Eo} \times 100$$

(%) または  $Dib = \frac{d}{Eo} \times 100$  (%) 式[18]

以上のように表しますが、これらの最大値をもって、単にディストーションとして表す こともあります。

# 10) 不整合反射減衰量 (Return Loss)

ディレイラインは一種の伝送ラインですから、同軸ケーブルなどの持つ特性インピーダンスと同様で、時間的・空間的に決まった一定の値を持っています。図3のように信号源インピーダンスと終端インピーダンスがディレイラインの特性インピーダンスに等しく整合されている場合は、ディレイラインの構成はLC回路網であるため内部では原理的にエネルギーの消費はなく、入力に与えられた信号は終端抵抗ですべて吸収され反射エネルギーはありません。つまり整合条件が成り立っているとき受端に最大エネルギーを伝送できることを示しています。反射の様子は複雑ですので図10に示します。この反射を応用するアプリケーションもあります。反射電圧は図4において、A点から送り出された信号は終端B点に達し、そこで反射された信号がA点に戻り印加している信号との合成波形がA点で観測されます。

不整合反射電圧Erefおよび、反射係数  $\rho$  は次のように求められます。

$$E_{ref} = E_i \times \frac{Rt - Zo}{Rt + Zo}$$

(V)  $\exists [19]$   $\rho = \frac{Rt - Zo}{Rt + Zo}$   $\exists [20]$

入力端に加えられる全エネルギーを*Pref*とし、不整合のために反射されるエネルギーを *Pr*としたとき、この比*Ar*を不整合反射減衰量と言い次のように表します。

$$Ar = 10 \log \frac{P_{ref}}{P_r} = 10 \log \frac{P_{ref}}{|\wp|^2 P_{ref}} = 10 \log \frac{1}{|\wp|^2} = 20 \log \left| \frac{Rt + Zo}{Rt - Zo} \right|$$

(d B)  $\vec{\mathbb{R}}[21]$

ディレイラインをカスケードに接続してトランスバーサルフィルタを構成するときなどは、この不整合反射減衰量の大きさが問題になります。通常のディレイラインでは特に指定しない限り不整合反射減衰量は20dB前後です。

| パルス幅                                                                                                                         | 図4A点での               |                                        |                                      |  |

|------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------------------------|--------------------------------------|--|

| 終端条件                                                                                                                         | Td>Pw                | 2Td <pw< th=""><th>B点での観測波形</th></pw<> | B点での観測波形                             |  |

| Rt=Zo                                                                                                                        | Ei->Pw               | <u>↓</u><br>Ei → Pw ←                  | A点と同じ波形 ↓<br>Pw ←> Ei                |  |

| Rt=0<br>終端短絡                                                                                                                 | Ei Pw                | Ei 2Td 2Td —Ei                         |                                      |  |

| Rt=∞<br>終端開放                                                                                                                 | Ei → Pw ← Pw 2Td     | 2Ei — (Pw-2Td)  Ei 2Td 2Td 2Td         | Pw ← 2Ei                             |  |

| Rt>Zo                                                                                                                        | Pw Pw V S            | Eref V Ei+Eref V Ei 2Td 2Td            | Pw ← Ei+Eref<br>Ei <eo< th=""></eo<> |  |

| Rt <zo< th=""><th>Pw ← -Eref  2Id → Pw</th><th>Ei 2Td 2Td V PW -Eref T</th><th>Pw &lt;&gt; Ei-Eref<br/>Ei&gt;Eo ↑</th></zo<> | Pw ← -Eref  2Id → Pw | Ei 2Td 2Td V PW -Eref T                | Pw <> Ei-Eref<br>Ei>Eo ↑             |  |

図10 反射波形の様子

# 11) 温度係数

ディレイラインの温度係数Tc は次のように定義します。

$$T_c = \frac{T_d - T_{do}}{T_{do}} \times \frac{1}{t - t_o} \times 10^6 = \frac{\Delta T_d}{T_{do}} \times \frac{1}{\Delta t} \times 10^6$$

(ppm/°C)  $\vec{x}$ [22]

Tdo : 基準温度 to における遅延時間 Td : to+t ( $^{\circ}$ ) における遅延時間

形状構造・回路構成・材料などにより異なりますが、一般的に±50~±200ppm/°C程度です。

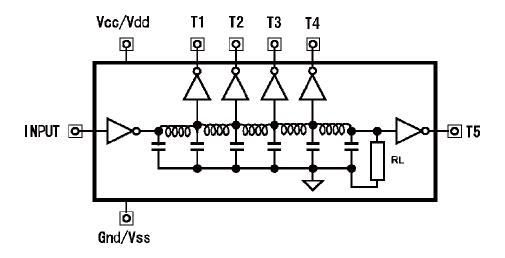

#### (8) ディレイラインモジュール

ディレイラインは図1に示したようにパッシブな回路網ですが、使用に当たっては入力端子・タップ端子に電子回路が付加されます。これらの影響により所定の遅延時間が維持できなくなることがあります。そのためディレイライン回路網と、ディジタルロジックゲートやアナログマルチプレクサなどを同一パッケージに組み込みモジュール化することで、これらの影響を吸収し、ファンアウトを拡大させることができ所定の遅延時間を持つロジックゲートICのように使用することができます。

1) TTL, CMOS, ECLゲート等との組み合わせモジュール。 そのモデル例を図11に示します。

図11 ディレイラインモジュール

図11のように、パッシブディレイライン、バッファーゲートIC、整合回路から構成されています。ゲートICはTTL, LVTTL, CMOS, ECL等の組み合わせが可能です。 バッファゲートがあるため従属接続の制限がありません。インターフェースは組み込まれているゲートICのインターフェース仕様になります。

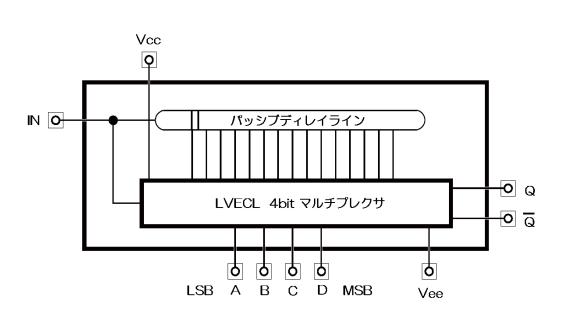

### (9) プログラマブルディレイラインモジュール

基本的には(8)項のディレイラインモジュールですが、バッファゲートの代わりにマルチプレクサー機能を持つゲートICと組み合わせ、アドレス信号により遅延時間を制御することができます。ディレイラインでは、遅延時間はタップの順位で選択しますので遅延時間の変更は接続タップを移動しなければなりません。

プログラマブルディレイラインモジュールでは、アドレス信号のビットコードで自由に制御することができます。また、アドレスのビットコードを固定すれば固定遅延となります。これもTTL、CMOS、ECL等のマルチプレクサーICと組み合わせたモジュールの構成が可能です。ここでは、LVECLを用いたアドレス4ビット制御の高速プログラマブルディレイラインモジュールのモデルを図11に示します。アナログスイッチのマルチプレクサーを使用すれば、アナログ信号のプログラマブルディレイラインモジュールの構成が可能です。

図12 プログラマブルディレイラインモジュール

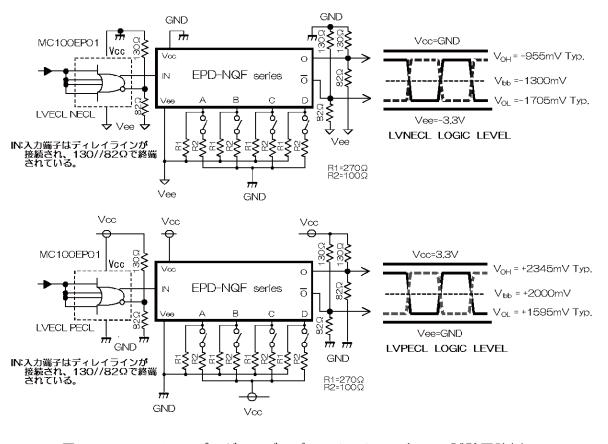

図13にこのモジュールの試験回路の例を示します。

図13 EPD-NQF プログラマブルディレイラインモジュール試験回路例

# (10) ディレイラインのアプリケーション

ディレイラインは、いろいろなアプリケーションが考えられますが、いくつかの原理的な応用例をご紹介します。

### 1) 基本的な応用例 (タイミング調整)

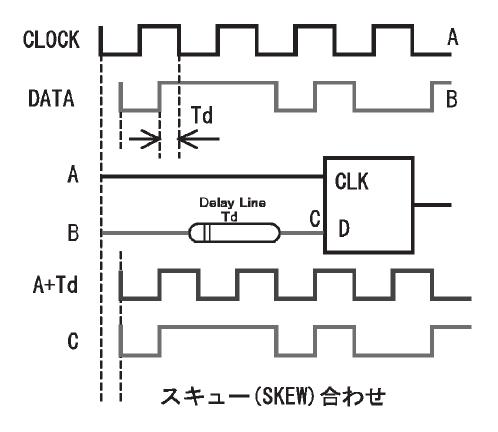

電子回路では、しばしばタイミング調整が必要なことがあります。異なった経路で電気信号を一致させたり、時間差が必要になったりします。このようなときディレイラインを信号ラインに付加することで、簡単に正確なタイミング調整ができます。ここではデータとクロック信号のスキュー合わせの様子を示します。高速になるほど、短い時間のずれが問題になります。

図14 データとクロックのスキュー合わせ

図14のようにデータとクロック信号が Td だけずれていた場合、これらのタイミングを一致させる必要があります。そこでB経路に遅延時間 Td のディレイラインを図14 のように付加します。Bの信号は Td だけ伝播が遅れます。その間クロック信号は Td 時間分進みますので、A・B信号間のスキュー合わせができることになります。

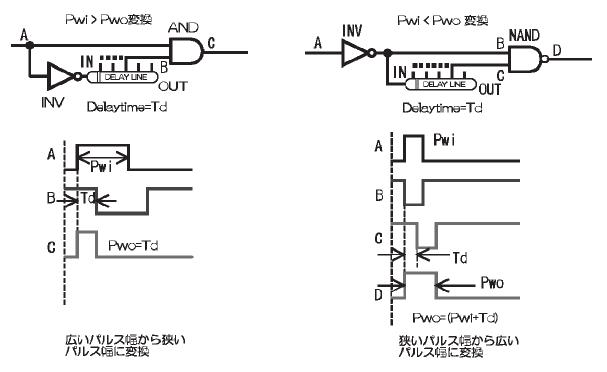

# 2) パルス幅の変換

図15 パルス幅の変換回路

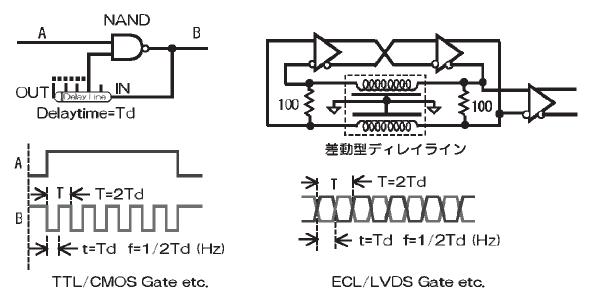

# 3) ディレイラインを用いた発振回路

図16 ディレイラインを用いた発振回路

容易に簡単な回路で安定した発振信号源が構成できます。正弦波にしたい場合は、発振 周波数の3倍で20dB以上減衰量の低域フィルタを付加します。

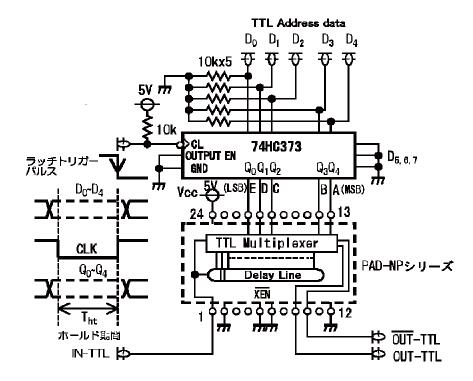

# 4) アドレスデータラッチ機能を持たせたプログラマブルディレイライン

図17 アドレスラッチ機能付加プログラマブルディレイライン

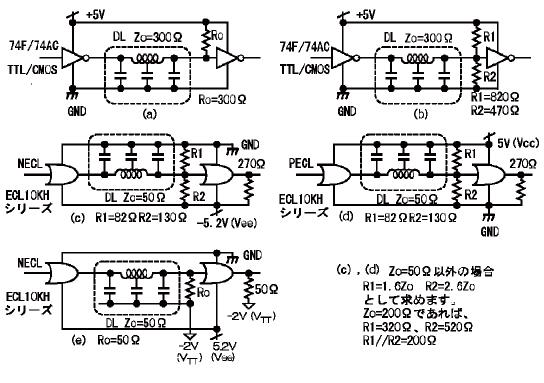

- 5) ディレイラインと各種ロジックファミリーとのインターフェース

- I) TTL, CMOSおよびECLロジックゲート

図18 ロジックゲートとディレイラインの終端例

ディレイラインの特性インピーダンスは一般に300 $\Omega$ 以下です。ディレイラインはその特性インピーダンスで終端しなければなりませんので、TTL,CMOSゲートでドライブするとき、シンク電流IOL およびソース電流IOH の規格による制限がありますので工夫が必要です。ECLゲートは50 $\Omega$ ラインをドライブできるので、ドライブ能力に関して問題はありません。しかし、ECLでは-2V、PECLでは+3VのVtt 電位を与えるか、または回路(b),(c),(d)のようなテブナン終端をします。いづれもRI とR2 の並列合成抵抗値はディレイラインの特性インピーダンスIOL に等しいことが求められます。(b)はゲート出力からディレイラインに流れ込む電流IOCH を小さく制御できます。

TTL, ECLにしても他にいくつかのロジックファミリがあります。その仕様とディレイラインの特性インピーダンスでドライブや終端の仕方が制限されますので、それを回避する方法を選ぶ必要があります。

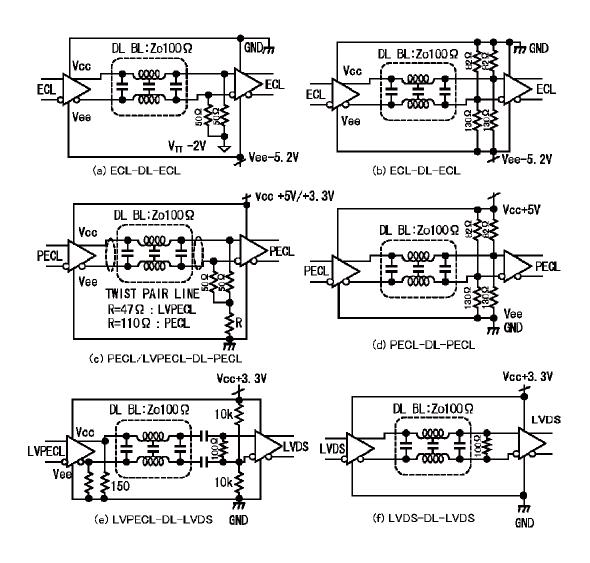

# Ⅱ) ディレイラインと差動型ドライバ・レシーバのインターフェース

図19 差動型ドライバ・レシーバと差動型ディレイラインの終端例

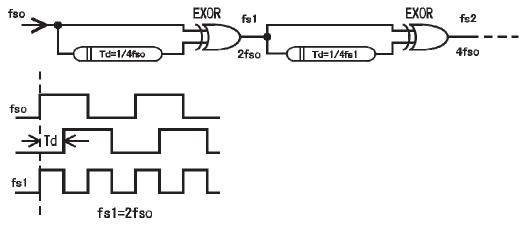

# 6) ディレイラインによる周波数マルチプライヤー

図20 周波数マルチプライヤー回路

図19は原理的なものですが、遅延時間を入力周波数の1/4波長にすると正確に2倍の周波数が得られます。カスケードにn段接続すれば、

$$fsn = 2^n f_{so}$$

式[23] となります。

デュティファクタはディレイラインの遅延時間精度によりますが簡単に周波数の逓倍ができます。

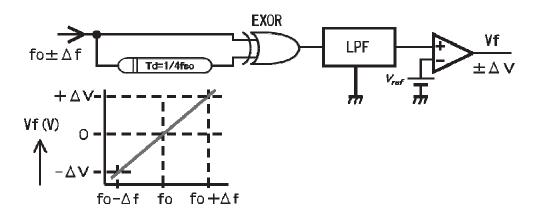

# 7) 周波数ディスクリミネータ

図21 周波数ディスクリミネータ回路

図20では入力周波数は固定ですが、図21では入力周波数はfo(Hz)を中心に±△f偏移します。偏移の方向および偏移量により出力パルスがパルス幅変調され、デュティファクタが変わります。この信号をLPFで積分すると図21のグラフのように周波数偏移と出力変位電圧のリニアな関係が得られます。これはドップラーレーダーや微小変位を周波数変調したレーザードップラー計などに応用されます。

### (11) おわりに

ディレイラインは電子回路で多様な分野に応用されていますが、電子デバイスの進歩と供に応用分野の変遷があり、かつてICメモリ周辺に大量に使用された最盛期と比べると市場は縮小していますが、依然としてエレクトロニクスの各分野で使用されています。 医用電子機器、超音波CT、X線CT、ソナー海洋機器、放送機器、レーダー機器、宇宙開発機器、電子線、放射能検出など原子力計装機器、通信伝送機器などがあります。また極めて短時間に起こる事象の観察には、正確なタイミングを合わせたトリガーパルスの発生にディレイラインは必要です。この他にトランスバーサルフィルタやディレイラインの反射を利用したクリッピング回路など応用範囲は多くあります。

カタログ品もご用意しておりますが、使用領域が多岐にわたっておりますので最適なものがご用意出来ていないことがあります。ディレイラインは構造的にカスタム仕様に対応できますので、お気軽に<ディレイライン・カスタム仕様パラメータシート>をご利用いただければ幸いです。

### 参考文献

1) Interfacing Between LVDS and ECL ON Semiconductor

- おことわり ここに記載のあるアプリケーションは参考用であり、回路の性能を保証するものではありません。ご使用にあたっては、必ず実際の回路での検証することをお奨めします。

- \*本資料の掲載内容の無断転用、複製、配布はお断り申し上げます。

# <ディレイライン・カスタム仕様パラメータシート>

| (1)     | ACTIVE DELAY LIN  | E             |      |       |    |    |     |

|---------|-------------------|---------------|------|-------|----|----|-----|

| 1)      | インターフェース          | LOGIC FAMILY  |      |       |    |    |     |

|         | 全遅延時間             |               | ±    |       | ns | or | μs  |

| 3)      |                   | タップ間遅延時間      | ±    |       | ns | or | μs  |

| 4)      | 供給電源電圧            | V             |      |       |    |    |     |

| 5)      |                   | MHz           |      |       |    |    |     |

| 6)      | 最小伝送パルス幅 _        | ns or $\mu$ s |      |       |    |    |     |

| 7)      | 適用規格              |               |      |       |    |    |     |

| 8)      | 形状・サイズ _          |               |      |       |    |    |     |

| 9)      | 具体的アプリケーシ         | /ョン           |      |       |    |    |     |

| 10)     |                   |               |      |       |    |    |     |

| (2)     | Passive DELAY LIN | ≣             |      |       |    |    |     |

| 1)      | 伝送インピーダンス         | ΩΩ            |      |       |    |    |     |

| 2)      | 全遅延時間             | <u></u>       | _± _ |       | ns | or | μs  |

| 3)      | タップ数              | タップ間遅延時間      |      |       |    |    |     |

| 4)      | 周波数特性             | MHz           | dB   |       |    |    |     |

| 5)      | 最大伝送信号レベル         | /dBm or       |      | V p-p |    |    |     |

| 6)      | 挿入損失              | dB or %以下     |      |       |    |    |     |

| 7)      | 絶縁耐電圧             | V DC          |      |       |    |    |     |

| 8)      | 絶縁抵抗              | MΩ以上          |      | V р-р |    |    |     |

| 9)      | 適用規格              |               |      |       |    |    |     |

| 10)     | 形状・サイズ _          |               |      |       |    |    |     |

| 11)     | <br>具体的アプリケーション   |               |      |       |    |    |     |

| 12)     | その他特記事項           |               |      |       |    |    |     |

| (3)     | 共通仕様              |               |      |       |    |    |     |

|         | 使用温度範囲            | ~℃   湿度範囲     |      | _~ _  |    | %  | R.H |

|         | その他使用環境条件         | =             |      |       |    |    |     |

|         | *不明な項目は記載         | 不要です          |      |       |    |    |     |

| <br>寺記事 | <br>項メモ           |               |      |       |    |    |     |

|         |                   |               |      |       |    |    |     |

|         |                   |               |      |       |    |    |     |

|         |                   |               |      |       |    |    |     |

|         |                   |               |      |       |    |    |     |

info@jpc-inc.co.jp TEL 03-3330-0823 FAX 03-3310-1870

お問合せ

| MEMO |  |

|------|--|

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

〒165-0032 東京都中野区鷺宮2-5-5 TEL.(03)3330-0823(代) FAX.(03)3310-1870 http://www.jpc-inc.co.jp/ E-mail:info@jpc-inc.co.jp

# JPC CO.,LTD

2-Chome 5-5,Saginomiya, Nakano-ku, Tokyo 165-0032 JAPAN TEL.+81-3-3330-0823 FAX.+81-3-3310-1870